# POLISH ACADEMY OF SCIENCE COMMITTEE FOR ELECTRONICS AND TELECOMMUNICATIONS

# ELECTRONICS AND TELECOMMUNICATIONS QUARTERLY

KWARTALNIK ELEKTRONIKI I TELEKOMUNIKACJI

VOLUME 54 - No 4

WARSAW 2008

#### EDITORIAL BOARDS

Chairman Prof. dr hab. inż. WIESŁAW WOLIŃSKI czł. rzecz. PAN

### Members of Editorial Board

prof. dr hab. inż. DANIEL JÓZEF BEM—czł. rzecz. PAN, prof. dr hab. inż. MICHAŁ BIAŁKO—czł. rzecz. PAN, prof. dr hab. inż. MAREK DOMAŃSKI, prof. dr hab. inż. ANDRZEJ HAŁAŚ, prof. dr hab. inż. JÓZEF MODELSKI, —czł. koresp. PAN, prof. dr inż. JERZY OSIOWSKI, prof. dr hab. inż. EDWARD SĘDEK, prof. dr hab. inż. MICHAŁ TADEUSIEWICZ, prof. dr inż. MARIAN ZIENTALSKI

EDITORIAL OFFICE

Editor-in-Chief

prof. dr hab. Inż. TADEUSZ ŁUBA

TECHNICAL EDITOR dr inż. GRZEGORZ BOROWIK

LANGUAGE VERIFICATION mgr JANUSZ KOWALSKI

RESPONSIBLE SECRETARY mgr ELŻBIETA SZCZEPANIAK

Address of Editorial Office 00-665 Warszawa, ul. Nowowiejska 15/19 Politechnika, pok. 484 Instytut Telekomunikacji, Gmach im. prof. JANUSZA GROSZKOWSKIEGO

> Editor-on-duty Mondays and Wednesday From 2pm to 4pm Phone number: (022) 234 77 37

Telephone numbers

Editor-in-chief: (022) 825 15 80; (022) 234 73 30

Responsible Secretary: 0500044131

www.tele.pw.edu.pl/keit

| Ark. Wyd. 8,00 Ark. druk. 7,00   | Podpisano do druku w lutym 2009 r. |

|----------------------------------|------------------------------------|

| Papier offset, kl. III 80 g. B-1 | Druk ukończono w lutym 2009 r.     |

Publishing Warszawska Drukarnia Naukowa PAN 00-656 Warszawa, ul. Śniadeckich 8 Tel./fsx 628-87-77

## IMPORTANT MESSAGE FOR THE AUTHORS

The Editorial Board during their meeting on the 18<sup>th</sup> of January 2006 authorized the Editorial Office to introduce the following changes:

### 1. PUBLISHING THE ARTICLES IN ENGLISH LANGUAGE ONLY

Starting from No 1'2007 of E&T Quarterly, all the articles will be published in English only.

Each article prepared in English must be supplemented with a thorough summary in Polish (e.g. 2 pages), including the essential formulas, tables, diagrams etc. The Polish summary must be written on a separate page. The articles will be reviewed and their English correctness will be verified.

### 2. COVERING THE PUBLISHING EXPENSES BY AUTHORS

Starting from No'2007 of E&T Quarterly, a principle of publishing articles against payment is introduced, assuming non-profit making editorial office. According to the principle the authors or institutions employing them, will have to cover the expenses in amount of 760 PLN for each publishing sheet. The above amount will be used to supplement the limited financial means received from PAS for publishing; particularly to increase the capacity of next E&T Quaterly volumes and verify the English correctness of articles. It is neccessary to increase the capacity of E&T Quarterly volumes due to growing number of received articles, which delays their publishing.

In case of authors written request to accelerate the publishing of an article, the fee will amount to 1500 PLN for each publishing sheet.

In justifiable cases presented in writing, the editorial staff may decide to relieve authors from basic payment, either partially or fully. The payment must be made by bank transfer into account of Warsaw Science Publishers The account number: Bank Zachodni WBK S.A. Warszawa Nr 94 1090 1883 0000 0001 0588 2816 with additional note: "For Electronics and Telecommunications Quarterly".

**Editors**

## Dear Authors,

Electronics and Telecommunications Quarterly continues tradition of the "Rozprawy Elektrotechniczne" quarterly established 54 years ago.

The E&T Quarterly is a periodical of Electronics and Telecommunications Committee of Polish Academy of Science. It is published by Warsaw Science Publishers of PAS. The Quarterly is a scientific periodical where articles presenting the results of original, theoretical, experimental and reviewed works are published. They consider widely recognised aspects of modern electronics, telecommunications, microelectronics, optoelectronics, radioelectronics and medical electronics.

The authors are outstanding scientists, well-known experienced specialists as well as young researchers — mainly candidates for a doctor's degree.

The articles present original approaches to problems, interesting research results, critical estimation of theories and methods, discuss current state or progress in a given branch of technology and describe development prospects. The manner of writing mathematical parts of articles complies with IEC (International Electronics Commission) and ISO (International Organization of Standardization) standards.

All the articles published in E&T Quarterly are reviewed by known, domestic specialists which ensures that the publications are recognized as author's scientific output. The publishing of research work results completed within the framework of Ministry of Science and Higher Education GRANTs meets one of the requirements for those works.

The periodical is distributed among all those who deal with electronics and telecommunications in national scientific centres, as well as in numeral foreign institutions. Moreover it is subscribed by many specialists and libraries.

Each author is entitled to free of charge 20 copies of article, which allows for easier distribution to persons and institutions domestic and abroad, individually chosen by the author. The fact that the articles are published in English makes the quarterly even more accessible.

The articles received are published within half a year if the cooperation between author and the editorial staff is efficient. Instructions for authors concerning the form of publications are included in every volume of the quarterly; they may also be obtained in editorial office.

The articles may be submitted to the editorial office personally or by post; the editorial office address is shown on editorial page in each volume.

**Editors**

### CONTENTS

| A. Szymański, E. Kurjata-Pfitzner: Amplitude comparator for self-calibration circuit of IR mixer | 469 |

|--------------------------------------------------------------------------------------------------|-----|

| M. Kachel: Performance of multichannel FX chip with DC Coupled schottky CdTe detector            | 483 |

| M. Damavandepeyma, S. Mohammadi: Asynchronous circuits through systemC description               | 493 |

| H. Niemiec, W. Kucewicz, M. Sapor, P. Grabiec, K. Kucharski, J. Marczewski, D. Tomaszewski,      |     |

| B. M. Amstrong, M. Bain, P. Baine, H. S. Gamble, S. L. Suder, F. H. Ruddell: SOI monolit-        |     |

| hic active pixel detector technology for improvement of I-V characteristics and reliability      | 507 |

| J. L. Fock-Sui-Too, B. Chauchat, S. Nicolau, F. Madrid, P. Austin, P. Tounsi, M. Mermet-         |     |

| -Guyennet: Experimenta study of power IGBT technologies at large range temperature               | 513 |

| A. Savakis, M. Lukowiak, J. Pyle: FPGA implementation of a lossless to lossy bitonal image       |     |

| compression system                                                                               | 533 |

| P. Pankiewicz, W. Powiertowski, G. Roszek: Hardware architecture of a parallel system for lane   |     |

| detection                                                                                        | 547 |

| L. J. Opalski: Numerical aspects of multiple-sensor measurements with potentiometric sensors5    |     |

| Information for the Authors                                                                      | 577 |

| Year contents of Electronics and Telecommunications Quarterly                                    | 581 |

| The List of the Reviewers                                                                        | 583 |

## Amplitude comparator for self-calibration circuit of IR mixer

### A. SZYMAŃSKI, E. KURJATA-PFITZNER

Department of Integrated Circuits and Systems, Institue of Electron Technology, Al. Lotników 32/46, Warszawa, Poland e-mail: aszym@ite.waw.pl, phone 22 5487 855 ekpf@ite.waw.pl, phone 22 5487 856

> Received 2008.09.10 Authorized 2008.11.03

This paper presents a new sequential amplitude comparator of two sinusoidal signals. It was designed for calibration circuit of phase shifters leading to better suppression of image component in the signal path of 2.4 GHz receiver. The experimentally obtained values of IRR above 45dB after calibration process indicate that image signal rejection is very good. It enables to conclude that the conception and design of amplitude comparator is suitable. The design was performed using SiGe 0,35µm BiCMOS process.

Keywords: Amplitude comparator, Self-calibration of IR mixer, Image rejection

### 1. INTRODUCTION

In wireless RF receivers with low IF (Intermediate Frequency)  $f_{IF}$ , suppression of image signals to acceptable level is difficult. It can not be done by application of high frequency filters due to small interval between useful and image frequencies, equal to  $2 \cdot f_{IF} \sim$  few MHz. Therefore special mixers are designed e.g. Hartley configuration, which eliminate (not totally of course) image signal by summing up the components of opposite phases and identical amplitudes. However effectiveness of this method depends strongly on process variations and amplitude / phase errors of heterodyne I/Q components. Hence to improve Image Rejection Ratio (IRR) an initial circuit calibration should be performed. It may be lead out [1] that

$$IRR \cong \frac{\left(\frac{\Delta V}{V}\right)^2 + \Delta \theta^2}{4},$$

where  $\frac{\Delta V}{V}$  is the relative amplitude error and  $\Delta \theta$  is phase error of I, Q components. Therefore the calibration process has to include two steps: amplitude balancing and phase correction.

In RF circuits a calibration process is implemented to assure stability of circuit parameters on process and temperature variations also. The calibration circuit is the integral part of receiver circuit. Usually a special RC calibration circuit with an external reference [2, 3] is applied. Sometimes a special calibration feedback loop is used [4] and [5].

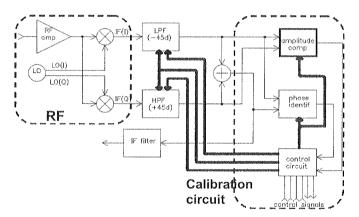

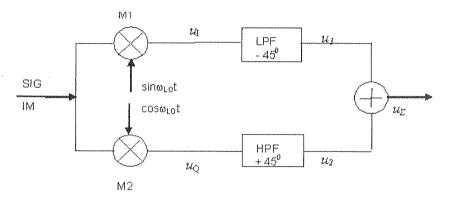

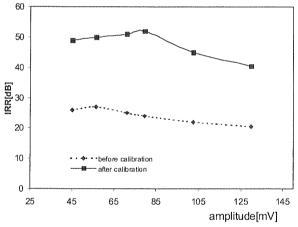

In the last paper the new, effective and simple method of self-calibration applied to the Hartley architecture mixer was presented. The circuit that implements this concept contains the amplitude comparator which indicates the relation between I and Q amplitudes of image signals and shows the tuning direction of phase shifters (Fig.1). The self-calibration process is driven by digital control circuit that produces appropriate control signals for tuning the capacitance arrays in phase shifters (LPF and HPF) depending on results of amplitude comparison and phase identification processes. The method was applied in the test chip that was designed for AMS BiCMOS 0,35 $\mu$ m SiGe process and prototyped via Europractice. The measurements show that the value of IRR was increased by ~20dB, to above 45dB which confirms the validity of this self-calibration method and also presented in this paper new concept of amplitude comparator.

Fig. 1. Self-calibration circuit architecture

The first section describes the elaborated self-calibration method, the second section describes operation of amplitude comparator, its subsections present simulation and experimental results and the last one conclusions.

cuit the nal [4]

d to ept am-The iate PF) The

nts. and

μm alue

this ude

ction and

### 2. SELF-CALIBRATION METHOD

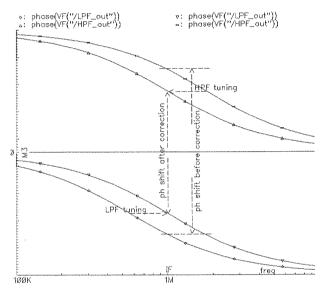

In Hartley architecture of an image-reject receiver a local oscillator with sine and cosine outputs and phase shifters  $\pm 45^{\circ}$  is used to obtain good image rejection (Fig.2). In theory the  $u_1$  and  $u_2$  components of the useful signal have identical amplitudes and phases while the image components which have reverse phases are rejected from the output spectrum after addition  $(u_{\Sigma})$ . The main drawback of this circuit is strong impact of mismatches on IRR. Process variations and parasitics existing in real circuits result in amplitude and phase errors at the adder inputs which leads to non-zero image signal on the output. In practice for integrated mixers IRR is limited to 20 dB and increasing its value is necessary.

Let's consider the circuit from Fig.2. Assuming the image components on the adder inputs:

Fig. 2. Hartley architecture of IR mixer, where SIG and IM are the input signal and its image respectively,  $\omega_{LO}$  is the pulsation of local oscillator signal

$$u_{1IM}(t) = U_{1IM} \sin \omega t$$

and (1)

$$u_{2IM}(t) = U_{2IM} \sin(\omega t + 180^0 + \Delta\Phi)$$

(2)

where  $\Delta\Phi$  is the phase error, we have on the adder output, approximately:

$$u_{\Sigma IM}(t) = (U_{1IM} - U_{2IM})\sin\omega t - U_{1IM}\Delta\Phi\cos\omega t. \tag{3}$$

Therefore to obtain high rejection of the image signal the equalization of the adder input amplitudes and compensation or minimisation of the phase error are necessary.

In practice the -45° and +45° phase shifters are realized as one-pole low-pass (LPF) / high-pass (HPF) filters whose magnitudes and phases of the transfer functions (in the ideal case) are as follows:

$$|A_{LPF}| = \frac{1}{\sqrt{1 + \left(\frac{\omega}{\omega_{pL}}\right)^2}}, \quad |A_{HPF}| = \frac{\frac{\omega}{\omega_{pH}}}{\sqrt{1 + \left(\frac{\omega}{\omega_{pH}}\right)^2}},\tag{4}$$

$$\Phi_{LPF} = arctg\left(\frac{\omega}{\omega_{pL}}\right), \quad \Phi_{HPF} = \frac{\pi}{2} - arctg\left(\frac{\omega}{\omega_{pH}}\right),$$

(5)

where  $\omega_{pL}$  and  $\omega_{pH}$  denote pulsations of the filter poles. Hence dependence (3) takes the form:

$$u_{\Sigma IM}(t) = (U_I|A_{LPF}| - U_Q|A_{HPF}|)\sin\omega t - U_I|A_{LPF}|(\Delta\Phi + arctg\frac{\omega}{\omega_{pL}} - arctg\frac{\omega}{\omega_{pH}})\cos\omega t$$

(6)

In the ideal circuit the produced relative phase shift is equal to 90° independently on the input frequency but the equality of  $U_{1IM}$  and  $U_{2IM}$  is achieved only for  $\omega_{pL} = \omega_{pH} = \omega_{IF}$  and  $U_I = U_Q$ . The process variations of R and C values that determine the time constants in the phase shifters cause that  $|A_{LPF}(\omega_{IF})| \neq |A_{HPF}(\omega_{IF})|$  which leads to inequality of amplitudes  $U_{1IM}$  and  $U_{2IM}$ . Moreover, the amplitude error of the local oscillator quadrature signals  $U_I \neq U_Q$  may occur. In this case in order to obtain amplitude balance the following equation has to be fulfilled:

$$|A_{LPF}(\omega_{IF})|U_I = |A_{HPF}(\omega_{IF})|U_Q$$

which will be valid for  $\omega_p = \omega_{pL} = \omega_{pH} = \omega_{IF} \frac{U_Q}{U_I}$ .

The relative phase shift between  $U_{1/m}$  and  $U_{2/m}$  may be compensated by creating the following corrective phase shift:

$$\Delta\Phi_{COR} = arctg \frac{\omega}{\omega_{pL}} - arctg \frac{\omega}{\omega_{pH}} = -\Delta\Phi \tag{7}$$

This will be achieved by moving the poles in the opposite directions from  $\omega_p$  by  $\pm\Delta\omega=\pm\frac{1}{2}\omega_{IF}tg\Delta\Phi$  (sign + for  $\omega_{pL}$  and sign – for  $\omega_{pH}$  when  $\Delta\Phi$  is small). The moving of poles does not change the amplitude balance when  $U_I=U_Q$ . For  $U_I=U_Q$  a small correction of the amplitude balance may be necessary.

It is clear from the above that the task of self-calibration process is to minimize the amplitude difference and phase error on the adder inputs. This can be achieved by proper shifting of the poles to get equal amplitudes and generate the phase correction  $\Delta\Phi_{COR}$ . It is realized by the tuning filters, which play role of phase shifters in I and Q mixer paths. Therefore the calibration process has to include two steps: amplitude balancing and phase correction.

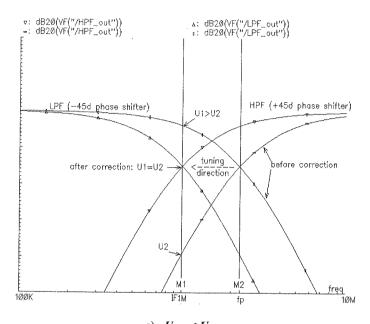

During the first step, the relation between amplitudes  $U_1$  and  $U_2$  determines the tuning direction of both shifters: for  $U_1 < U_2$  we have  $f_p > f_{IF}$  ( $f_p$  – pole frequency) and the

(4)

T.Q.

(5)

akes

$s \omega t$

(6)

y on

nine hich

f the

otain

g the

(7)

$p_p$  by

The

$=U_Q$

mize ed by

ction

I and

itude

ıning

d the

pole frequency of each phase shifter has to be decreased (Fig.3a) until the amplitude balance will be achieved, otherwise both pole frequencies have to be increased (Fig. 3b)

Fig. 3. The tuning of phase shifters during amplitude balancing

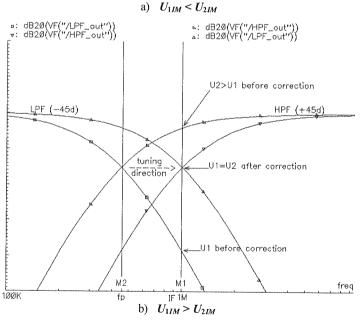

Similarly, during the second step the directions of the filter tuning are determined by comparing the phase relation between the  $u_1$  and  $u_{\Sigma}$  signals. After achieving the amplitude balance we may assume  $U_{1IM} = U_{2IM} = U$ , therefore according to (3)

$$u_{\Sigma IM}(t) = -U \mid A_{HPF} \mid \Delta \Phi \cos \omega t,$$

(8)

which gives:  $u_{\Sigma IM} \div \cos \omega t$ , for  $\Delta \Phi < 0$ , and  $u_{\Sigma IM} \div -\cos \omega t$ , for  $\Delta \Phi > 0$ , while  $u_1(t) = U_{1IM} \sin \omega t$ .

The adder output signal  $u_{\Sigma IM}$  is shifted  $\pm 90^{\circ}$  to its input  $u_1$ . The recognition of this phase makes the correct tuning of shifters possible until the change of  $u_{\Sigma IM}$  phase will be noticed. This event stops the phase correction step. Fig.4 illustrates the idea of the phase error correction by tuning both shifters in opposite directions.

Fig. 4. The idea of relative phase shift correction

In the case of  $\Delta\Phi > 0$  the pole frequency of + 45° shifter (HPF) has to be decreased and the pole frequency of – 45° shifter (LPF) has to be increased. In the opposite case the change of tuning directions of the phase shifters is required.

A convenient method of phase shifter tuning is digital control of capacitances creating its time constants. However, it introduces an unavoidable error associated with the LSB step. Let's consider the maximum value of the errors for amplitude and phase correction due to the smallest capacitance change  $\Delta C$ . In the vicinity of the pole the change of output amplitude due to  $\Delta C$  is expressed as follows:

$$\Delta U_1 = U_I \cdot \frac{d|A_{LPF}|}{dC} \Big|_{\omega = \omega_p} \cdot \Delta C = -\pi U_1 f_{IF} R \Delta C, \tag{9}$$

ned the

(8)

n of ase

hile

a of

ased case

nces ated and

pole

(9)

$$\Delta U_2 = U_Q \cdot \frac{d|A_{HPF}|}{dC} \Big|_{\omega = \omega_p} \cdot \Delta C = \pi U_2 f_{IF} R \Delta C. \tag{10}$$

Since both shifters are tuned simultaneously and the amplitude balance will be identified by the change of relation between U1 and U2, the maximum relative error of amplitude balance on the adder inputs is described as follows:

$$\frac{\Delta U}{U} = \left| \frac{\Delta U_1}{U_1} \right| + \left| \frac{\Delta U_2}{U_2} \right| = 2\pi f_{IF} R \Delta C, \tag{11}$$

where other possible sources of errors are neglected.

Similarly, for the phase changes caused by the phase shifters LPF and HPF when the capacitance value is changed by  $\Delta C$  we have respectively:

$$\Delta\Phi_{LPF} = \Delta C \cdot \frac{d\Phi_{LPF}}{dC} \Big|_{\omega = \omega_p} , \qquad \Delta\Phi_{HPF} = \Delta C \cdot \frac{d\Phi_{HPF}}{dC} \Big|_{\omega = \omega_p}$$

(12)

Taking into considerations that the tuning during the phase correction is carried in the opposite directions, the full phase change due to  $\Delta C$  step is  $\Delta \Phi_c = 2\pi f_{IF} R \Delta C$ .

Assuming IF frequency  $f_{IF} = 1 \text{MHz}$ ,  $R = 8.8 \text{k}\Omega$ ,  $\Delta U/U = 1\%$ ,  $\Delta \Phi = 0.5^{\circ}$  we obtain the maximum LSB capacitances  $\Delta C_1 = 180 \text{fF}$  for amplitude balancing and  $\Delta C_2 = 160$  fF for phase correction. It should provide IRR not worse than 45dB after the calibration process.

The application of the calibration method described above is limited by the minimum value of the switched capacitance used in the capacitance arrays, which depends on parasitic capacitances of the switches. It also limits the IF frequency to few MHz. Increase of the number of bits results in increase of capacitance arrays which leads to the increase of integrated circuit area.

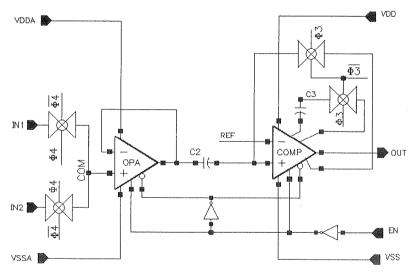

### 3. AMPLITUDE COMPARATOR

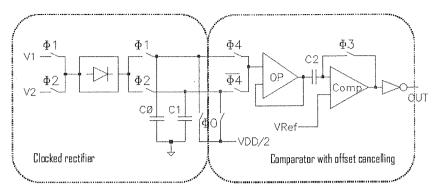

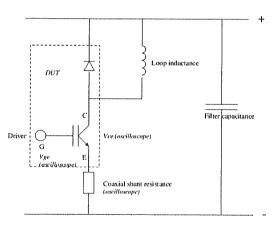

The task of the amplitude comparator is to establish the relation between amplitudes of I, Q components on adder inputs (Fig.1) and to generate information which of them is greater. The concept of the comparison of two amplitudes of IF (1 MHz) sinusoidal waves relies on rectifying, storing and providing the DC voltages to the inputs of comparator with offset cancellation (Fig.5a). The circuit is controlled by the five-phases clock, which is generated by digital control circuit presented in [5]. The relations between phases are shown in Fig.5b.

In the circuit only one two-half rectifier is used. It is sequentially switched between two sinusoidal voltages V1, V2 and two identical storage capacitors C0, C1 (Fig.5a). Such solution allows avoiding an error caused by two different offset voltages of two amplifiers and rectifiers.

Fig. 5a. Simplified diagram of amplitude comparator

Fig. 5b. Phases  $\Phi 0 - \Phi$  4 used to control comparator work

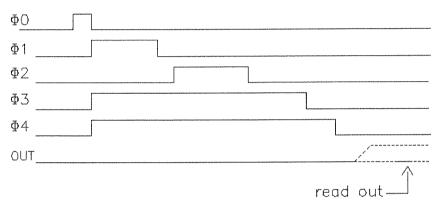

Input voltages V1 = A1 - A2 and V2 = B1 - B2 (Fig.6) are attached to the inputs of differential amplifier via two pairs of switches controlled by phases  $\Phi$ 1,  $\Phi$ 2. Each of them closes the switches for 5 IF periods (5µs).

The third pair of switches controlled by  $\Phi = \overline{\Phi 1 + \Phi 2}$  delivers to the differential amplifier DC voltages (D1, D2) identical with DC components of input sinusoidal voltages. Such solution allows avoiding a substantial recharging of input serial capacitors (Fig.6) and therefore eliminates the source of additional errors. The output of the differential pair is connected to the two-half transistor rectifier that is supplied with current source 15 nA. Its output (RECT), via identical switches, at phases  $\Phi 1$  and  $\Phi 2$ , is sequentially connected to the identical capacitors C0 and C1 (7 pF). They keep the values of DC voltages for the comparation time. After comparison cycle is finished these capacitors are discharged to the VDD/2.

E.T.Q.

oidal paciof the with d Φ2, op the ished

Fig. 6. Differential clocked recitifier

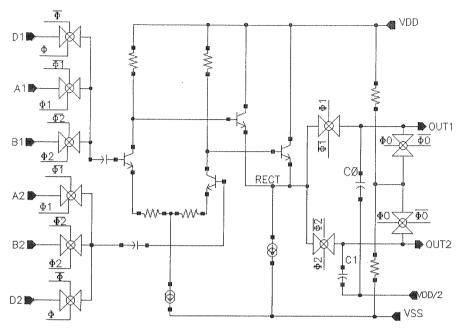

Next the voltages stored on C0 and C1 are delivered to the comparison circuit via the operational amplifier OPA in the follower configuration. The follower prevents discharging of C0 and C1 when they are connecxted to the capacitor C2 = 10 pF (Fig.7), what would introduce the additional error.

Fig. 7. Comparator with offset cancellation

The comparator COMP is a typical 3-stages one: the first stage is differential; the second stage contains frequency compensation circuit, which is connected during phase  $\Phi 3$  to avoid circuit oscillation while the feedback loop is closed. The third stage has push-pull configuration.

During phase Φ3 capacitor C2 is charged to:

$$V_{C2} = V_{C0} + V_{offOP} - (V_{REF} + V_{offCOMP})$$

, where

$V_{offOP}$ ,  $V_{offCOMP}$  are the offset voltages of opamp and comparator respectively. After switching the comparator input from  $V_{C0}$  to  $V_{C1}$  the comparator negative input voltage will take the value:

$$V = V_{C1} + V_{offOP} - V_{C2} = V_{C1} - V_{C0} + V_{REF} + V_{offCOMP}.$$

Then the comparator differential input voltage will be as follows:

$$V_{inCOMP} = V_{REF} + V_{offCOMP} - V = V_{C1} - V_{C0}$$

It clearly shows that reference voltage  $V_{REF}$  and offsets of opamp and comparator do not influence the comparation result, assuming they are constant during comparison cycle. The possible errors may result from charge injection effect during the switches opening.

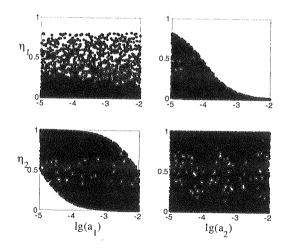

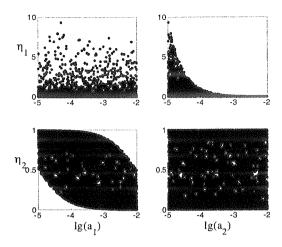

### 3.1. SIMULATION RESULTS

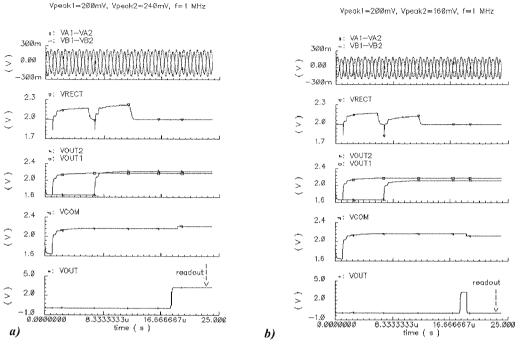

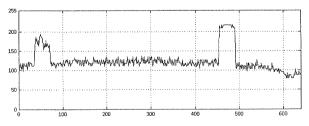

The amplitude comparator was simulated with *spectre* using foundry models of all devices. Fig.8 presents voltages at selected nodes to detailed illustration of circuit operation: differential sinusoidal input voltages are rectified giving VRECT that sequentially charges capacitors C0, C1 and produces VOUT1 and VOUT2 voltages at the rectifier outputs. Next, voltage on comparator input buffer VCOM and comparator output VOUT are shown. The last voltage is read out by the digital control circuit at the end of each measurement cycle and is used at amplitude balancing process.

cond 3 to pull

After tage

r do ison ches

s of reuit t sees at rator iit at

Fig. 8. Simulation results – amplitudes of compared signals (f = 1 MHz) 200 mV and a) 240 mV – output state OUT = 1; b) 160mV – output state OUT = 0

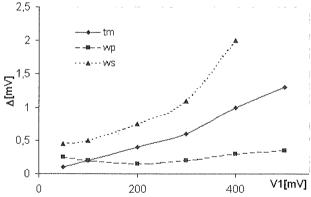

Accuracy of comparation is very important because it determines the ability of image signal suppression. Therefore dependence of resolution of compared input signal amplitudes on value of the input amplitude was simulated (Fig.9).

Fig. 9. Dependence of the resolution  $\Delta$  of amplitude differences on value of this amplitude. Corner analysis

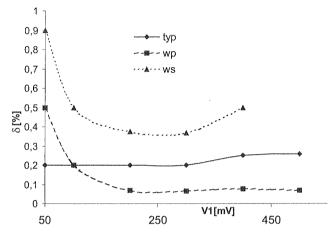

For amplitude values expected in the system up to  $\sim 200 \text{mV}$ , the minimum resolution is better than 0,5mV. For amplitude equal 50mV the resolution  $\Delta = 0,1 \text{mV}$  and is greater for greater signal amplitudes. The relative resolution  $\delta$  defined as the ratio of resolution  $\Delta$  / amplitude [%], is independent on amplitude until 300mV (Fig.10). But even for the worst corner parameters the resolution is quite enough to use the presented amplitude comparator for balancing the amplitude of I, Q signals delivered to adder in receiver signal paths.

Fig. 10. Relative resolution  $\delta$  of input amplitude differences. Corner analysis

### 3.2. EXPERIMENTAL RESULTS

The main goal of the measurements was to check the validity of self-calibration method of mixer with low IF = 1 MHz. The test chip was equipped with some test pins to IF path but the direct measurements of amplitude comparator were not predicted. It was planed to investigate the full calibration algorithm and the amplitude and phase calibrations separately also. Therefore full information concerning the amplitude calibration process was available.

The measurements were performed using two sets of sinusoidal 1 MHz input signals:  $I(0^{\circ})$ ,  $Q(-90^{\circ})$  and  $I(0^{\circ})$ ,  $Q(+90^{\circ})$  with various amplitudes enforced on I/Q paths of IF circuit. These signals were generated in external auxiliary circuit that allow to adjust amplitudes and phases. The measurements set up with application board were described in [5].

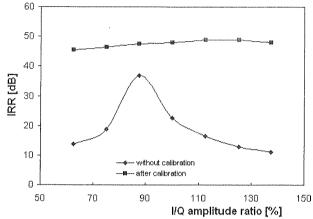

First the IRR without and with activated amplitude calibration for zero phase error as a function of starting amplitude imbalance (ratio of I and Q component) were measured. The results (Fig.11) confirm proper operation of the amplitude self-calibration algorithm because it increases the suppression of the image signal substantially: IRR is increased even by 35dB in the case of great initial imbalance and reaches 48dB.

ation

and is

a of

But

ented

dder

The best results of IRR after amplitude calibration were obtained for initial I/Q amplitude ratio in the range 95 - 125 %.

Fig. 11. Measured IRR when only amplitude calibration was performed in the case of phase error=0

Next it was interesting to measure how the calibration of amplitude affects IRR dependence on value of input voltage amplitudes (Fig.12). The best result was obtained for I/Q amplitudes in the range 60 - 80 mV.

Fig. 12. Changes of IRR versus input amplitudes of calibrated signal. Phase error = 0. Only amplitude calibration was executed

The measurements indicate that the amplitude calibration process goes worse in the case of small and big magnitudes. It is nearly obvious because for small signals the absolute values of possible errors play more important role. In the case of great amplitudes a generation of harmonics of basic 1 MHz may cause an additional error.

The measurement results of IRR, performed before and after calibration process, proved the conception and the realization of the amplitude comparator presented in this paper.

ation e test edice and itude

nals: of IF djust ribed

error meation IRR 8dB.

### 4. CONCLUSIONS

The presented amplitude comparator was applied in the self-calibration circuit of IR mixer. It applies sequential rectifying, storing and comparison of input signals which allow to eliminate differences, which may be introduced by two separate circuits for two compared signals.

The simulations results indicate very good comparison accuracy of I and Q image components, better than  $\delta$ =0,2% for typical parameters.

The amplitude comparator was applied in the self-calibration circuit of IR mixer. The test chip measurements provided IRR better than 20dB in comparison to IRR before calibration and reach the value of 48dB. It confirmed the validity of the concept and the design of the presented amplitude comparator.

### 5. ACKNOWLEGMENTS

The Polish Committee of Scientific Research under Grant nr 4 T11B 03825 supported this work.

### 6. REFERENCES

- 1. B. Razavi: RF Microelectronics, Prentice Hall PTR.

- 2. H. Darabi, et al.: A 2.4-GHz CMOS Transceiver for Bluetooth, IEEE J. of Solid-State Circuits, Vol. 36, 2001, pp. 2016-2024.

- 3. H. Darabi et al.: A Dual-Mode 802.11b/Bluetooth Radio in 0.35mm CMOS, IEEE J.of Solid-State Circuits, Vol.40, 2005, pp. 698-705.

- 4. T. Das, et al.: Self-Calibration of Input-Match in RF Front-End Circuitry, IEEE Trans. On Cir. & Syst.II, Vol.52, 2005, pp. 821-825.

- 5. A. Szymański, et al.: *The self-calibration method of IR mixer with low IF*, Analog Int. Cir. & Signal Proc., vol.55, nr 2, 2008, pp.115-124.

T.Q.

it of hich for

nage

The fore and

sup-

s,Vol.

-State

Cir. &

Cir. &

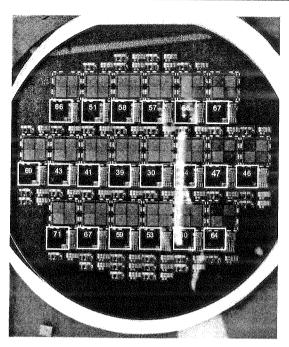

# Performence of multichannel FX chip with DC coupled Schottky CdTe detector

M. KACHEL

Department of Measurements and Instrumentation AGH University of Science and Technology, al. Mickiewicza 30, 30-059 Krakow, Poland e-mail: maciej.kachel@agh.edu.pl

Received 2008.08.29 Authorized 2008.10.15

This paper describes the performance of multichannel ASIC (called FX) which has been connected to Schottky CdTe detector by DC coupling. Because of DC coupling, leakage current of the detector flows into readout electronics and changes its performance. The I-V characteristic of CdTe Schottky detector with guard ring have been measured and we have performed both simulation and experimental verification of FX IC behavior vs. detector leakage current. Due to the low values of this detector leakage current (140 pA for bias voltage of 700 V) performance of FX IC is slightly influenced. Measurements performed with low values of detector's leakage current (below 1 nA), show that the gain of readout channel stays constant with changes of leakage current, while the offset voltage at the discrimonator input changes linearly of about 4.5 mV per 100 pA of the detector leakage current. Limitations of DC coupling method are shown based on measurements with Schottky CdTe detector without guard ring, which produces higer leakage current.

Keywords: CdTe detector, Schottky, CdTe, DC coupled, Multichannel ASIC, CSA, PZC

### 1. INTRODUCTION

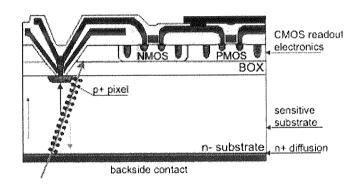

Cadmium Telluride (CdTe) detectors are very attractive for X-ray medical applications because of their large bandgap energy that allows us to operate detector at room temperature. Their high atomic numbers ( $Z_{Cd} = 48$ ,  $Z_{Te} = 52$ ) lead to high absorption for high energy X-ray [1]. In recent years pixel CdTe detectors have been widely used, especially in medical imaging applications [2]. To read signals from pixel detector, multichannel readout electronics are needed.

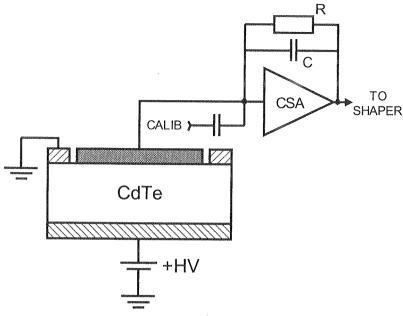

The goal of the reported research was to test the performance of multichannel ASIC chip – FX24 for operation with DC coupled CdTe detector having in mind future medical applications. The FX chip was proven to work correctly with AC coupled Si strip detectors. However, in the case of CdTe DC coupled detector, the front-end electronics should sink detector leakage current and this could influence the parameters of the readout electronics.

In this work we present leakage current measurements of Schottky CdTe detector with guard ring, simulations of the performance of a single channel of the FX chip with the detector leakage currents. We also give detailed description of measurements of Schottky CdTe detector connected with the FX chip. Finally we show the limitations of DC coupling, using for this Schottky CdTe detector without guard ring.

### 2. DETECTOR TESTS

Standard CdTe detectors which are built as structures of Pt/CdTe/Pt suffer from charge loss which reduces its energy resolution. This is caused by the low mobility and short lifetime of holes  $(10^{-5}-10^{-4}~{\rm cm}^2{\rm V}^{-1})$  compared to the lifetime of electrons  $(10^{-4}-10^{-3}~{\rm cm}^2~{\rm V}^{-1})$  [3]. This low mobility of holes results in charge loss, which together with large detector's leakage current, affects the performance of the readout electronics and reduces energy resolution of the total system.

However, CdTe Schottky detectors have been introduced, with leakage current strongly suppressed. Schottky CdTe detector is a structure of In/CdTe/Pt where indium is used as the anode electrode and Pt as cathode electrode for p-type CdTe semiconductor. Schottky barrier is formed at the In/CdTe interface, so one can operate detector as a Schottky diode. After biasing the detector (by applying several hundred of volts), leakage current is two orders of magnitude smaller than in standard Pt/CdTe/Pt detectors. Due to low leakage current CdTe Schottky detectors can be operated at high electric fields, which allow full charge collection.

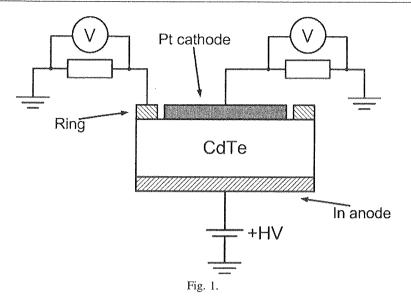

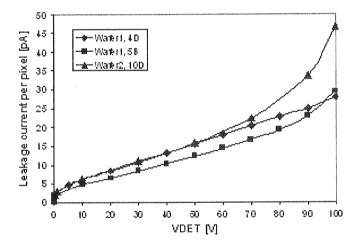

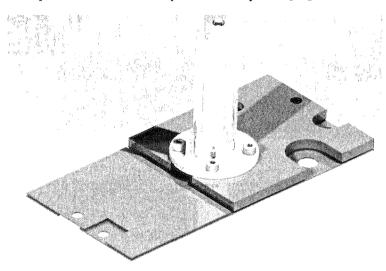

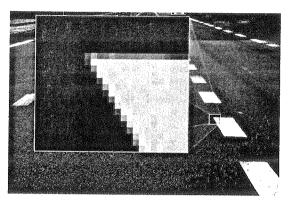

In our test we have used CdTe Schottky detector with guard ring [4] from ACRO-RAD Company [5]. The detector is 1 mm thick, its size is 6.1×6.1 mm<sup>2</sup>, and cathode electrode has a size of 4×4 mm<sup>2</sup>. To obtain its leakage current characteristics, I/V measurement has been made in configuration shown in Fig. 1.

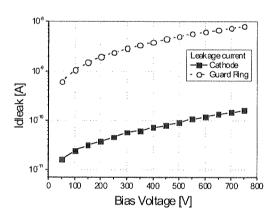

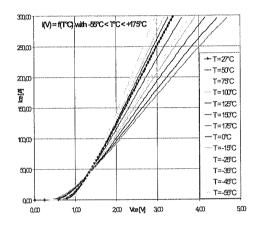

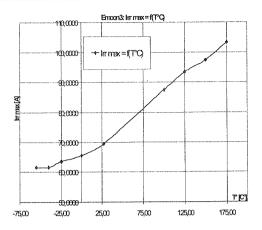

Detector was reverse biased by connecting high voltage source from anode's side. Cathode current, as well as ring current, were measured using indirect method of current measurement, the measurements were performed at room temperature. Figure 2 presents measured I/V characteristics of leakage currents of central electrode and guard ring. As it can be seen applying guard ring to the Schottky CdTe detector, causes cathode leakage current to be in pA range (120 pA for 700 V bias), which is at least 10 times less than in standard CdTe detectors [6]. Such low value of leakage current makes this detector a good candidate for DC coupling connection.

SIC ture oled end ters

ctor chip ents lons

rom

ility

cons

nich

dout

rent

indTe

rate

d of

e/Pt

nigh

ROnode I/V

side.

d of

gure

and

ctor,

ch is

kage

Fig. 2.

### 3. READOUT ELECTRONICS

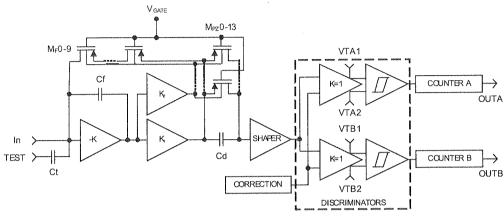

The FX IC is a 24 channel readout ASIC designed and fabricated in CMOS 0.35  $\mu$ m process [7]. Fig. 3 presents block diagram of a single readout channel of the FX chip. Each channel is built of charge amplifier (CSA) followed by pole zero cancellation circuit (PZC), a CR-RC<sup>2</sup> shaper, two discriminators and two 20 bit counters.

Charge sensitive amplifier (CSA) is based on folded cascode configuration with PMOS as an input transistor of W/L = 420  $\mu m$  / 0.35  $\mu m$ . Capacitance  $C_f$  of 100 pF together with channel conductance of parallel connected PMOS transistors array MF0-9 working in triode region provide feedback loop for CSA. Source follower  $K_1$  provides

output resistance of the CSA stage of about 0.5 k $\Omega$ . The PZC cancellation circuit consists of capacitance  $C_d$  connected in parallel with fourteen PMOS transistors  $M_{PZ}0$ -13 operating in triode region.

Fig. 3.

Bulks of  $M_F$  and  $M_{PZ}$  transistors are connected to CSA output through the source follower  $K_2$ , therefore the bulk voltage tracks changes of CSA output. Effective resistances of CSA feedback and PZC circuit can be controlled in a wide range (several  $M\Omega$  to tens of  $G\Omega$ ) by the internal 5-bit DAC. Pulses after second order shaper stage with a peaking time  $T_P=75$  ns are selected by two discriminators according to their amplitude.

Such circuit works properly even up to about 2 MHz of average rate of input pulses. The noise performance measured with AC coupled silicon strip detector ( $C_{DET} = 1 \text{ pF}$ ) is below 150 electrons rms.

Because CSA, shaper and discriminators are DC coupled, and the common threshold level is applied to the multichannel system, a problem of the DC level spread at the discriminator inputs has been solved by the implementation of a correction DAC in each channel. Correction offset can be set up in range of 60 mV with 7 bit precision it is implemented in each channel independently. This can be helpful in operation with DC coupled strip or pixel detector where we expect the spread of the detector leakage current between the channels.

# 4. SIMULATIONS OF READOUT ELECTRONICS WITH A DC COUPLED DETECTOR

Presented circuit was simulated with the use of HSPICE software. Input of CSA was triggered with square current pulses (1 ns rise and fall time, 9 ns pulse width) with various amplitudes to simulate an injection of holes (or electrons). Voltage response at

the tron dur leal

Vol.

the

in t

set 50.4

In 10 out vol det As to for

mu

con-0-13

]→ atuo

]→ OUTB

ource resiveral stage their

ilses. l pF)

thread at DAC ision with kage

CSA with

ise at

D

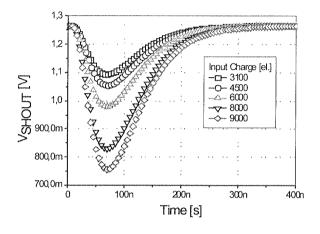

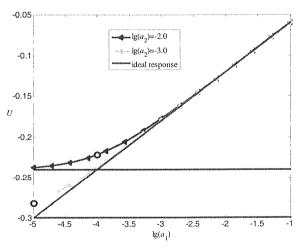

the shaper output for positive input current signals with different amplitudes is shown in the picture below (Fig. 4). In these simulations the detector leakage current was set to zero. The gain of the front-end electronics calculated from these simulations is  $50.4~\mu\text{V/el}$ .

Fig. 4.

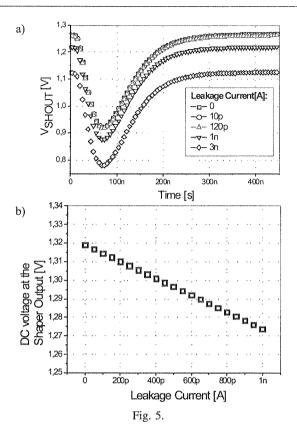

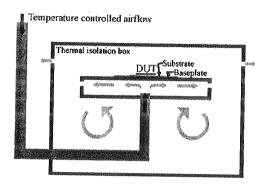

Because readout electronics is DC coupled with the detector, leakage current from the detector modifies its parameters. Simulations of leakage current influence on electronics performance were done by adding DC detector leakage current component during the HSPICE simulation. Figure 5a shows shaper output for different values of leakage current.

It can be observed that the offset voltage shifts with the increase of leakage current. In the range of leakage current 0-3 nA offset voltage changes by 112 mV (about 10 %) for setting the CSA feedback resistor to tens of M $\Omega$ . Also the amplitude of output signal changes but only by 2 mV (about 0.6 %), so the changes in the offset voltage are of the main importance. However, in the range 0-160 pA of presented detector leakage current (Fig. 5b) offset voltage changes only by 8 mV (about 0.6 %). As it was mentioned, a correction circuit is present in FX chip to reduce channel to channel DC level spread at the discriminator input. However, it can also be used for suppressing offset voltage caused by the spread of the detector leakage current is multichannel system.

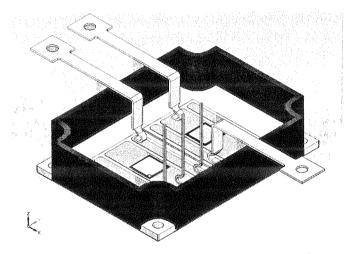

# 5. MEASUREMENTS OF SCHOTTKY CDTE DETECTOR WITH GUARD RING CONNECTED TO FX INTEGRATED CIRCUIT

Detector's cathode was connected to single channel of FX ASIC by DC coupling (Fig. 6). Guard ring of the detector was connected to ground potential. Anode electrode was supplied with high voltage. Input signals for readout electronics were generated by on-chip internal calibration circuit.

This configuration assures that leakage current of cathode electrode of the detector flows into readout electronics, therefore influence of leakage current can be measured.

Because the FX circuit has a binary architecture, the basic analogue parameters (offset, gain) can be obtained by scanning the threshold of discriminator for a given amplitude of input pulses. At the output we measure the fraction of pulses which exceed the discriminator threshold and trigger the comparator.

va me vo

of lin of puthe car

pe

Fig. 6.

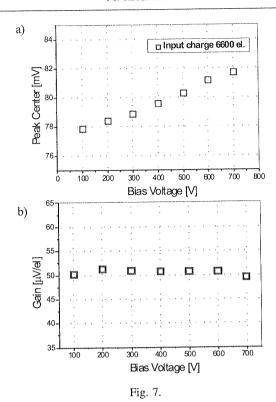

Measurements were performed for different values of leakage currents and different values of amplitudes of input signals. Making a threshold scan and differentiating the measured integral distribution we find the peak positions for different values of bias voltages.

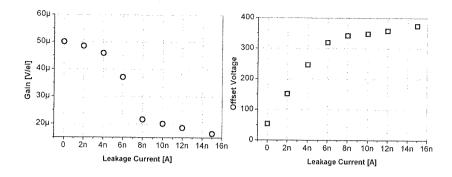

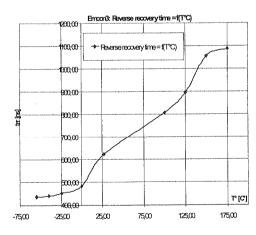

For given amplitude of input pulses the peak position shifts as the bias voltage of the detector increases from 100 V to 700 V. The changes of the peak position are linear and for the leakage current changes from 25 pA to 140 pA peak position changes of about 6 mV (Fig. 7a). From the measurements with different amplitudes of input pulses we find the gain of our readout electronics. The gain (Fig. 7b) is constant in the range of applied detector's bias voltage. It means that the shift of peak position is caused by the DC level voltage shift at the shaper output and the measured shift of peak position is in a good agreement with earlier simulations.

NG

ling ode ated

ctor red. eters iven hich

Vol.

wei was

cha

det 200

det so . The

SM

leal

aro

## 6. DC COUPLING TECHNIQUE LIMITATIONS DUE TO HIGH DETECTOR LEAKAGE CURRENT

For some applications DC coupling may not be suitable because of large leakage current of the detector (in range of few nA). One of the reasons of leakage current rise may be a need to use the detector without guard ring. Detectors without guard ring are needed when they are used in matrix of sensors, where guard rings would cause dead space in the detector's area, decreasing its performance.

Having in mind future applications, simulations of FX24 readout electronics and measurements with CdTe Schottky detector without guard ring were made to determine how large values of detector's leakage current influence the readout performance.

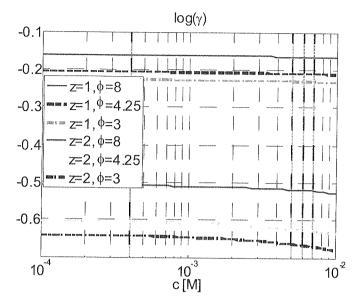

From the simulations performed it can be observed (Fig. 8) that with detector leakage current rising up to a few nA, gain of readout electronics drops (by 3 % for 2 nA, up to 60 % for 10 nA) and significant shift of offset voltage is present (from 150 mV for 2 nA up to 350 mV for 10 nA).

Fig. 8.

For measurements Schottky CdTe  $4\times4$  pixel detector was used. The detector is 1 mm thick, its size is  $4\times4$  mm<sup>2</sup>. This detector did not have a guard ring. Firstly, five channels of the detector were DC coupled with the FX24 chip. The rest of channels were left floating.

Large shift of offset voltage (around 300mV) and gain drop (down to 30  $\mu$  V/el) was observed from X-ray measurements (X-ray beam energy - 18keV) performed with detector bias voltage equal to 200 V. Noise estimated from calibration pulses is around 200 el., noise estimated from X-ray measurement is around 250 el.

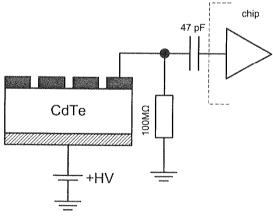

The same detector was connected to the FX chip via AC coupling (Fig. 9), using SMD capacitor (47 pF) and SMD resistor (100 M $\Omega$ ). Thanks to the AC coupling large detectors leakage current does not influence the performance of readout electronics, so large values of bias voltage can be applied to increase detector's charge collection. The gain from measurements is estimated to 51 V/el., which is the same as with low leakage current DC coupled version. Noise calculated from X-ray measurements is around 146 el.

Fig. 9.

OR

akage t rise ring cause

s and rmine c. tector % for

(from

### 7. SUMMARY

The performance of the FX integrated circuit working with DC coupled CdTe Schottky detector was presented. Simulations of FX single readout channel were performed with the use of HSPICE software to determine the influence of leakage current on channel parameters. After connecting the detector to FX chip, measurements were performed. The data obtained from measurements matches with simulations confirming that low leakage current (below 1 nA) of CdTe Schottky detector, equipped with guard ring, have very little influence on FX chip parameters.

However, leakage current of few nA and more causes degradation of FX chip performance, making DC coupling not suitable for this application. As it was presented, AC coupling connection between the detector and readout chip can be used to suppress the influence of leakage current.

### 8. ACKNOWLEGMENTS

This research and development project was supported by Polish Ministry of Science and Higher Education in the years 2008-2010.

The author wishes to express his gratitude to Prof. Paweł Gryboś from AGH UST, for his valuable suggestions and support.

### 9. REFERENCES

- Tanaka, Y. Kobayashi, T. Mitani, K. Nakazawa, K. Oonuki, G. Sato, T. Takahashi, S. Watanabe: Recent achievements of the high resolution Schottky CdTe diode for γ-ray detectors, New Astronomy Reviews, 48, pp. 269-273, 2004.

- 2. M. Chmeissani, C. Frojdh, O. Gal, X. Llopart, J. Ludwig, M. Maiorino, E. Manach, G. Mettivier, M. C. Montesi, C. Ponchut, P. Russo, L. Tlustos, A. Zwerger: First Experimental Tests with a CdTe Photon Counting Pixel Detector Hybridized with a Medipix2 Readout Chip, IEEE Trans. Nucl. Sci., vol.51, pp. 2379-2385, 2004.

- 3. T. Takahashi, B. Paul, K. Hirose, C. Matsumoto, R. Ohno, T. Ozaki, K. Mori, Y. Tomita: *High-resolution Schottky CdTe diode for hard X-ray and gamma-ray astronomy*, Nucl. Instrum. Methods, vol. A 436, pp. 111-119, 1999.

- 4. K. Nakazawa, K. Oonuki, T. Tanaka, Y. Kobayashi, K. Tamura, T. Mitani, G. Sato, S. Watanabe, T. Takahashi, R. Ohno, A. Kitajima, Y. Kuroda, M. Onishi: Improvement of the CdTe Diode Detectors using a Guard-ring Electrode.

- 5. ACRORAD Corporation, www.acrorad.co.jp, Japan

- 6. P. Fischer et al.: A Counting CdTe Pixel Detector for hard X-ray and Gamma-ray imaging, IEEE Trans. Nucl. Sci., vol.48, pp. 2401-2404, 2001.

- 7. P. Grybos, R. Szczygiel: Pole-Zero Cancellation Circuit With Pulse Pile-Up Tracking System for Low Noise Charge-Sensitive Amplifiers, IEEE Trans. Nucl. Sci., vol. 55, pp. 583-590, 2008.

designing the control of control

glob

CdTe perrrent were

ming guard

chip nted,

press

Asynchronous Circuits through SystemC Description

MORTEZA DAMAVANDPEYMA, SIAMAK MOHAMMADI

School of Electrical and Computer Engineering, University Of Teheran {mdamavand, smohammadi}@ece.ut.ac.ir

> Received 2008.08.28 Authorized 2008.11.04

Asynchronous design is fundamentally different and not yet a well-established methodology. An important obstacle to growth of this methodology is lack of CAD tools to design circuit automatically. The starting point in developing a circuit is its modeling and simulation. At this paper we will propose an asynchronous library as extension to SystemC language to enable asynchronous circuit description at the highest level of abstraction. For this purpose, channel, join, fork, mux, demux, and merge that are basic elements of asynchronous circuits are introduced into the library. Also a tool was developed which extracts optimized control flow graph and data flow graphs from the high level description. By using proposed library modeling and designing of efficient asynchronous circuits can be done without having to deal with detail of asynchronous implementations. Extracted CFG and DFG were prepared in well-defined form that can easily be used for synthesis purpose, verification or test generation in later steps of our digital design flow.

Keywords: Asynchronous Circuit, SystemC, High-Level Modeling, CFG and DFG Extraction

### 1. INTRODUCTION

As CMOS manufacturing technology scales into deep and ultra-deep sub-micron design, problems with clock skew, clock distribution, and on-chip communication in high-speed synchronous designs are becoming increasingly difficult to overcome. On the other hand, general interest for embedded and portable systems enforces the designers to think about on power metric in the design. In addition to this difficulty, design of complex System-On-Chip structures in VLSI circuits produces new challenges. At this high massive integration level synchronizing all blocks of a large SoC to a unique global clock definitely decreases the performance of digital system and the clock di-

ience

UST,

S a t o, diode

n o, E.

o s, A.

ed with

Mori, Nucl.

tani, la, M.

, IEEE

System 8. stribution tree should expand in all over the SoC, so has a lot of overhead in wiring, area, and power in digital system.

Asynchronous circuits have potential advantages to become an option in various application areas. One of the biggest claims to fame for asynchronous logic is that it consumes less power due to the absence of a clock. Other advantages of asynchronous circuits are low latency, higher performance, and lower electromagnetic interference. However, there are some obstacles that avoid asynchronous design to become a feasible solution. One of the most important problems is the lack of appropriate CAD tools. Designers have to use synchronous tools with tricky modifications to fool them into thinking that the design is synchronous, making logic design verification, timing rollups, and race condition checks messy and involved.

Almost all of the languages for asynchronous circuit designs are based on CSP [1] that hides the details of handshaking protocols.CHP [2], Balsa [3], OCCAM [4] and Tangram [5] are other examples of asynchronous language. Most of existing languages for asynchronous system design have different structure from well-known synchronous system design language (e.g. Verilog or VHDL), so they are specific for asynchronous design and could not be used instead of synchronous language. Also their simulation tools are not completely available. In spite of traditional CSP based languages for asynchronous circuits other effort was also done previously. Hofer et al. [6] present an asynchronous SystemC library to model asynchronous circuits and especially NoCs. They introduced some style in SystemC like handshaking, channels, parallel operators and arbiter that is useful for describing NoC structures. In [7] a method for synthesizing object oriented structures in SystemC to achieve synchronous circuits was presented.

To overcome difficulty in modeling and simulating asynchronous circuits we propose an asynchronous library for SystemC [8] language. In addition to this library, a tool which extracts control-data flow structure from Asynchronous-SystemC is presented. A readable intermediate representation for this flow is proposed to accommodate the design specification with the vision of optimization capabilities in the conversion step.

Section 2 discuss on features of the SystemC in describing digital circuits, especially asynchronous circuits. Proposed library components will be illustrated in Section 3. Section 4 expresses steps involved in extracting Control Data Flow structures from Asynchronous SystemC Code. Section 5 contains related case study to demonstrate the features of our modeling strategy and the conclusion will be drawn in last section.

### 2. FEATURE OF SYSTEMC IN MODELING DIGITAL CIRCUITS

### 2.1. SYSTEMC POTENTIALITY

SystemC is a system design language based on C++ that has been developed in response to the need for a language capable of improving the overall productivity for designers of electronic systems. Strictly speaking, SystemC is not a language, but

rathe C++ polyr and s featu

Vol. 5

mode tivity elabo proce featur at run dersta syster produ [10]. guage featur dule

betwe

In that e shakin there one si this tr it must taken non-b

A some the fir

for me

and hat these

ring,

rious

hat it

nous

ence.

a fe-

CAD

them

ming

P[1]

and

rather a class library within a well established C++ language. Hence every feature of C++ can be used in modeling hardware. Some C++ features like object oriented and polymorphism enable the designer to use this concept in SystemC to model circuits and simulate them with available tools. Another superiority of SystemC is the Template feature and parameterized hardware description, which enables the reusability of design compared to common HDLs.

SystemC provides event objects and dynamic sensitivity to facilitate hardware modeling in behavioral model and concurrent software. Most HDLs offer static sensitivity: process respond to events on input signals and ports that are predetermined at elaborate time. In addition to the static sensitivity, SystemC offers dynamic sensitivity: processes can wait explicitly on events that are determined at run-time [9]. We use this feature to promote our asynchronous circuit modeling to synchronize hardware blocks at run-time. This higher level of abstraction gives the design team a fundamental understanding early in the design process of the intricacies and interactions of the entire system and enables better system tradeoffs, better and earlier verification, and overall productivity gains through reuse of early system models as executable specifications [10]. SystemC provides mechanisms crucial to modeling hardware while using a language environment compatible with software development. Major hardware-oriented features implemented within SystemC include: Time model, Hardware data types, Module hierarchy to manage structure and connectivity, Communications management between concurrent units of execution, Concurrency model [10].

### 2.2. WEAKNESS OF SYSTEMSC IN MODELING ASYNCHRONOUS CIRCUIT

In asynchronous design there is no global synchronization clock signal; meaning that every module operates separately and the synchronization is performed by handshaking signals. Handshake signals can be modeled by channels in SystemC, although there are some points that must be considered. Suppose that in the handshake channel, one side put data and the other side takes data when it becomes available. For modeling this transaction we need a channel that doesn't store data in a buffer (in other words it must be memory less). Also the first side must block further action until the data is taken at the other side. Native SystemC uses sc\_signal or sc\_fifo; however the former is non-blocking and the latter is not memory-less so they do not satisfy the requirement for modeling an asynchronous handshaking.

According to the asynchronous technique requirements, in handshaking modules some refined channels are necessary to model one-to-many and many-to-one channels; the first is to implement the fork operation and the second the join operation.

A strong point of SystemC is its simulation kernel that enables us to create events and handle synchronization. In the following section we will propose a way to solve these issues.

uages onous onous lation es for ent an NoCs. rators sizing

nted. ropoa tool ented. te the step. espeection from

te the

on.

ped in etivity ge, but

### 3. COMPONENT OF LIBRARY

SystemC implements a discrete time computation model. Processes are basic units of concurrent activities and are grouped into modules. Modules can contain other modules, allowing the hierarchical construction of the system model. Processes communicate with each other via interfaces, channels and ports, and can synchronize with each other via events objects. Interfaces define a set of related communication methods. An interface defines an abstract type, and does not implement any functionality. Ports are declared as being associated with a particular interface. The port's methods call the methods of the interface. Channels implement one or more interfaces. When connecting two modules together, the channel could offer one interface to one module, while offering a different interface to another.

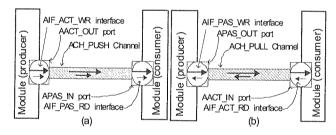

In the asynchronous circuits an active process initiates a transaction by sending a request signal to the passive process. Active and passive processes bind to each other using channels. An active process may put data into a channel or get data from it. According to the direction of the request signal and data we categorize channels into two types: Push and Pull channels where in the first one the direction of the request signal and data is the same.

### 3.1. INTERFACES

According to the above categorization, for the process type (active or passive) and the operation on channel (write or read), we define four interfaces for asynchronous channels:

- AIF\_ACT\_WR: Asynchronous active write interface

- AIF\_PAS\_ WR: Asynchronous passive write interface

- AIF\_ACT\_RD: Asynchronous active pull interface

- AIF\_PAS\_RD: Asynchronous passive pull interface

Fig 1. shows the implementation code of AIF\_ACT\_WR. In Fig 1., put provides a method to initiate the transaction, probe provides a method to verify the channel status to know if the data are taken at other side. rd\_event returns an event when the pull side of the channel picks the data. write\_block is a method that uses the above methods to perform a blocking write in the push channel.

```

template<class T>

class AIF_ACT_WR: virtual public sc_interface{

public:

virtual void put(const T& data) = 0;

virtual bool probe() = 0;

virtual const sc_event& rd_event() const = 0;

virtual void write_block(const T& data) = 0;

};

```

Fig. 1. Implementation of active write interface

mc

0

tio

and and Fig

We

chr tha of imp

and so units other

com-

n menality. thods When

odule, ling a

other om it. s into equest

e) and onous

ides a status Il side ods to

#### 3.2. PORTS

Ports to a module are like pins to a chip that enable communication between modules. According to the section 4.1 categorization we need four port types:

- AACT\_OUT: Asynchronous active output port

- APAS\_IN: Asynchronous passive input port

- AACT\_IN: Asynchronous active input port

- APAS\_OUT: Asynchronous passive output port

All implementations are template based increasing the reusability of the description.

#### 3.3. CHANNELS

Channel between modules is like the interconnection and buses between chips. We implement two types of channel: ACH\_PUSH and ACH\_PULL channels. The first channel is a class that derives from AIF\_ACT\_WR and AIF\_PAS\_RD interface classes and implements their virtual methods. The pull channel derives from AIF\_PAS\_WR and AIF\_ACT\_RD interface classes. Fig 2. presents a diagram of these concepts. In Fig 2. the larger arrow shows the direction of data and the smaller arrow represents the request signal direction.

Fig. 2. Diagrams of (a) a push channel (b) a pull channel

#### 3.4. SYNCHRONIZATION MODULES

In the previous subsection, we presented a method to model asynchronous synchronization between two modules. Now, we present the synchronization among more than two channels. Also we introduce the modeling methodology for building blocks of asynchronous circuits [20], which are a minimum set of components sufficient to implement asynchronous circuits that contain latches, function blocks, unconditional and conditional flow controls. The first and second are similar to synchronous circuits, so we describe the third and fourth.

#### 3,4.1. UNCONDITIONAL FLOW CONTROL

Fork and join components are used to handle parallel threads of computation. Forks are used when the output from one component is input to more components; Joins are used when data from several independent channels needs to be synchronized – typically because they are (independent) inputs to a circuit. A merge component has two or more input channels and one output channel. Handshakes on the input channels are assumed to be mutually exclusive and the merge relays input tokens/handshakes to the output. For each of these components we present a class where their data type is template class, increasing their flexibility. Fig 3. presents an example of a join operation that synchronizes two input stream handshakes since their outputs are synchronized.

```

#include <systemc.h>

#include "asynch.h" // defined in our library

#include "JOIN.h" // defined in our library

int sc main (int argc, char *argv[])

{// Module instantiation

producer<char> prA("RandomGen1");

producer<int> prB("RandomGen1");

consumer<char> coA("consumer1");

consumer<int> coB("consumer2");

// Channel instatiata on

ACH PUSH<char> A("ch1"), Async b("ch2");

ACH PUSH<int> B("ch2"), Bsync_a("ch4");

// synchronization operation instantiation

JOIN<char,int>

join("join1");

//Module Binding

prA(A);

prB(B);

join(A, B, Async b, Bsync a);

coA(Async b);

eoB(Bsync a);

sc start(-1);

return 0;

```

Fig. 3. Synchronize channel A & B by Join

#### 3.4.2. CONDITIONAL FLOW CONTROL

MUX and DEMUX components perform the usual functions of selecting among several inputs or steering the input to one of several outputs. These components like the unconditional flow control can be described in our library to ease asynchronous circuit modeling in SystemC. Fig 4. shows the implementation of a two-input MUX in our library for push channels. We assume that all three inputs must become available, before the output of MUX becomes active.

forl the

fun we ma mo

use wri ME

PA:

wit to ( ation. nents; onized nt has annels kes to ype is ration ized.

```

class ADD_SUB: public sc module

public:

APAS IN<sc uint<8>> A.B:

APAS IN<bool>

AACT OUT<sc uint<8>> R1,R2;

SC HAS PROCESS(ADD SUB);

ADD SUB(sc_module_name name): sc_module(name)

SC_THREAD(func1); }

void funcl(){

sc uint<8> a.b.r1.r2:

bool c:

while (true) {

/*Parallel Passive read*/

while(!(A->probe()&&B->probe()&&C->probe()))

wait(A->wr_event()|B->wr_event()|C->wr_event());

A->get(a); B->get(b); C->get(c);

/*Function block*/

if(c){ r1=a+b; r2=a-b; } else { r1=a-b; r2=a+b; }

/*Parallel Active Write*/

R1->put(r1); R2->put(r2);

while(R1->probe() || R2->probe())

wait(R1->rd event()|R2->rd event());

void func2(){

sc uint<8> a,b,r1,r2;

bool c:

while (true) {

PAR_PAS READ(A, a, B, b, C, c);

if(c)\{ r1=a+b; r2=a-b; \} else \{ r1=a-b; r2=a+b; \}

PAR_ACT_WRITE(R1,r1,R2,r2);

}};

```

Fig. 4. Implicit synchronization inside the function body

#### 3.4.3. IMPLICIT FLOW CONTROL

An inter-module synchronization was presented by using explicit modules (join, fork, etc.) in the last two subsections. A flexible way is to synchronize channel inside the modules, we call it implicit synchronization.

Fig 4. presents an example that implements an arithmetic module. There are two functions (func1 and func2) in Fig 4. with the same functionality. In the first function we use the raw capability of our library, whereas in the second one we use some macros to handle synchronization between channels. Although the first method needs more lines of code, it is more flexible than the second one. MERGE, PAR\_PAS\_READ, PAR\_ACT\_READ, PAR\_PAS\_WRITE and PAR\_ACT\_WRITE are macros that could be used to handle synchronization implicitly. The last four macros were used to read or write the variables in function body from or to channels in parallel. Parameters of MERGE macro is a series of input channels and a variable. The macro sets variables with the activated channel number. For example, in the following line sel\_var is set to 0, if ch1 becomes active, or it is set to 2 if ch3 becomes active. In all cases the variable out is set to the activated channel content.

among ts like ronous UX in ilable, MERGE(ch1,ch2,ch3,ch4,sel\_var,out);

The first four macros can be used to implement an unconditional flow control whereas the MERGE macro is used to implement a conditional flow control inside the modules.

## 4. CONTROL DATA EXTRACTION FROM ASYNCHRONOUS SYSTEMC LIBRARY

#### 4.1. SYNTHESIZABLE CONSTRUCTS

The presented tool extracts control and data flow structures from SystemC 2.0.1 constructs complemented with asynchronous library described in previous section. Hierarchical description can be done by using SC\_MODULE constructs in SystemC. A repeated sequential task is modeled by means of functions.

According to the asynchronous circuit properties, the communication is modeled with dynamic sensitivity; thus we employ SC\_THREAD construct in SystemC to model concurrent blocks inside the module. Concurrent blocks are composed of instantiated modules and SC\_THREAD blocks; these asynchronous blocks communicate with each other through asynchronous channels. Inside each concurrent block, there exist sequential constructs such as if-then-else, switch-case, for-loop and function call.

#### 4.2. INTERMEDIATE REPRESENTATION

The extracted control flow determines the execution order of constructs in sequential bodies (function or sc\_thread), as well as blocks dependencies in concurrent bodies (sc\_module). The extracted data flow represents arithmetic and logical operations. It is composed of operational nodes and their operands edges.

#### 4.2.1. CONTROL FLOW

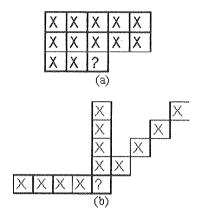

Intermediate representation for control structures is composed of two types: hierarchical and sequential constructs. Fig 5. shows hierarchical constructs, MOD for module declaration, FUN for function declaration, THR for sc\_thread declaration and MDI for module instantiation are used.

th ab ch

> th 6. ta "j

> > da

aı

"I w in ntrol e the

2.0.1 ction. emC.

deled nodel tiated each sequ-

quenodies . It is

ierarodule OI for

| MOD;id;chan_list  | MDL;idport_list            |

|-------------------|----------------------------|

| /Anoduk body      | chan_list := (chan)+       |

| DOM;              | chan := type wilth name;   |

| FUN;id,param_list | type = PIPO AIAO           |

| /function body    | port_list := (port)+       |

| NUF;              | port = width;name;         |

| THR;il;           | param_list.= (param)+      |

| /thread body      | param := dir,width,name    |

| RHT:              | dir = input put put incout |

| P-ELL,            |                            |

Fig. 5. Hierarchical control structures

'+' expresses one or more iteration, and '|' states alternation between choices. In these structures "id" is a unique number at each level of hierarchy. The "width" in above constructs presents data width of channels, ports or parameters. The "type" of channels is shown with PI (passive in), PO (passive out), AI (active in) and AO (active out).

| if_control;id;dfgld;dfgPortList; { if;id;dfgld,variable;     //sequential body     fi; }+     RETURN;id;dfgld;dfgPortList;      bop;id;dfglD;dfgPortList;     //sequential body     pool;     PAR_PAS_READ;id;chanVarList; | dfgPortList.=(dfgPort)+ dfgPort:=dir.param dr =IN OUT paramList.=(param)+ param:= variabk konstant chanVarList.= (chanVar)+ chanVar.=chanmel.variable |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                            | CALL;id;fmld;paramList;  CALL;id;fmld;paramList;                                                                                                      |  |

| PAR_ACT_READ;id;chanVarList;<br>PAR_PAS_WRITE;id;chanVarList;<br>PAR_ACT_WRITE;id;chanVarList;                                                                                                                             |                                                                                                                                                       |  |

Fig. 6. Sequential control structures

Sequential constructs are used inside the body of FUN and THR blocks, where their order is important in data flow. Fig 6. depicts sequential control structures. In fig 6. "id" represents the order of constructs. The construct "if" is used for the implementation of if-then-else or switch-case structures, for each of these construct there is an "if\_control" node and some "if" constructs. In "if\_control" dfgId is the ID number of data flow graph used for evaluation of conditions and dfgPortList contains its inputs and outputs. The body of "if" is executed when "variable" evaluates to a non-zero value. All "if" constructs which are in the same group, have identical "id" numbers. "PAR\_X\_X" constructs represent channel operations that read channels to variables or write variables to channels. "RETURN" is used inside the function in place of "return" in SystemC, "loop" is used for iterative constructs, a DFG is used to compute the loop condition, and "VA" is used for variable assignment. In these constructs dfgId is the ID of DFG that computes an expression with its parameters in dfgPortList. "CALL" constructs are used for function calls where "funId" is the called function ID.

#### 4.2.2. DATA FLOW

The extracted data flow is shown by means of Data flow Graph (DFG) where nodes represent arithmetic or logical operations and edges show the flow of data. Each DFG has an ID that maps to a construct in the control flow.

#### 4.3. IMPLEMENTATION

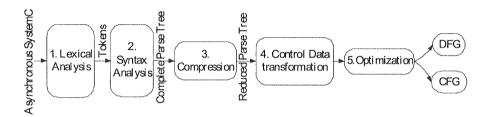

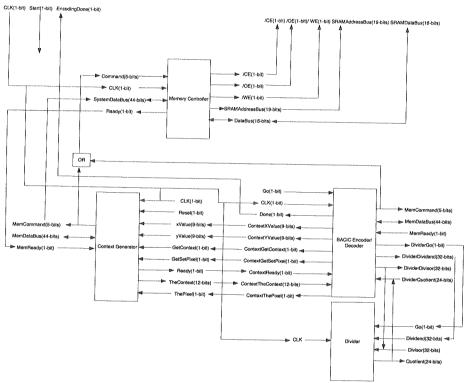

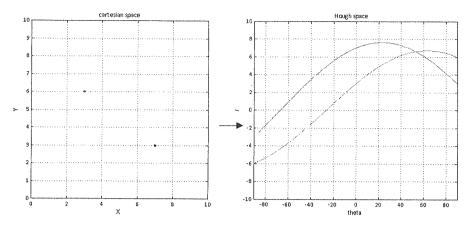

The flow-graph representation of the high-level description is obtained by parsing the input Asynchronous SystemC code. Fig 7. depicts the various steps involved in this methodology. These steps are quite similar to the phases of a compiler, each of which transforms the source program from one representation to another.

Fig. 7. Steps involved in Control Data extraction

The lexical analysis phase translates the source program into a stream of tokens, where each token is a sequence of characters with collective meaning, such as an identifier, a keyword, an operator or a punctuation character. This stream of tokens is further subjected to syntactic analysis which imposes a hierarchical structure on them to verify the syntax of the program. The codes from these two phases are generated by applying the standard compiler construction tools, Lex and Yacc.

The parsing of the tokens using YACC code imposes a hierarchical structure that could be visualized as a tree-structure (parse tree). The parse tree that is assumed to be available is just a conceptual visualization of the syntactic structure of the program. Explicit codes are required to extract such a parse tree from the YACC code. Specific C++ codes were used for this purpose in our tool. The parse tree, thus obtained, is further compressed to obtain a syntax tree in which the operators appear as the interior nodes, and the operands of an operator are the children of the node for that operator. The syntax tree is transformed, through another C++ code, into the final control and data flow graph that depicts the total flow of the control and data in the original description. Finally some optional optimization can be applied to meet design constraints in the compilation step.

dire ever tech sim

Vol.

sior grap loop nex This ope to p bloom

are

chro bloc wer asyr of v

thes

here

Each

rsing

this

hich

Table 1

#### 4.4. OPTIMIZATION

Behavioral optimization can be implemented in different ways. It can be applied directly to the parse tree, or during the generation of the intermediate format, or even on the intermediate format itself, according to different cases. Most optimization techniques change control and data flows separately, but some of them affect both flows simultaneously. We use both of these groups in our tool.

The tree-height reduction, constant and variable propagation, common sub-expression elimination and dead code elimination techniques can be applied to data flow graphs. The control flow graphs can be optimized by imposing function flattening and loop unrolling. Another optimization is applied in our tool, which will be useful in next steps (e.g. synthesizing) that combine multiple DFGs to form one single DFG. This optimization affects both CFGs and DFGs, where by increasing the number of operational units in DFG, resource sharing capability increases. This method applies to parallel blocks within sequential bodies like the case blocks of a switch construct or blocks of if-then-else constructs. The complexity of this method is O(n), where n is the number of blocks in the intermediate code of CFG. The effects of these optimizations are verified in next section.

#### 5. EXPERIMENTAL RESULTS

For proving the effectiveness of our method for modeling and simulation of asynchronous circuits in SystemC we choose JPEG encoder, which is composed of various blocks and is a suitable case to show the synchronization between modules. All blocks were implemented with our library in SystemC and are connected to each other through asynchronous channels. Table 1 presents the number of SystemC lines of code, number of words and characters. Comments and blank lines in the source are not included in these numbers.

Report of JPEG implementation in SystemC

|                | #LINES | #WORDS | #CHARECTERS |

|----------------|--------|--------|-------------|

| RGB_2_YCbCr    | 53     | 197    | 1226        |

| DCT            | 75     | 283    | 1597        |

| Quantization   | 53     | 200    | 1267        |

| Zig Zag Scan   | 93     | 247    | 1781        |

| Encoder        | 128    | 329    | 2207        |

| Entropy Coding | 63     | 143    | 1270        |

| Total          | 465    | 1399   | 9348        |

kens, as an ens is them rated

e that ed to gram. ecific ined, s the r that final n the

esign

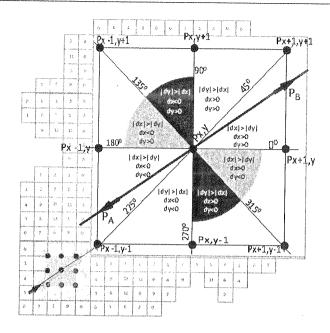

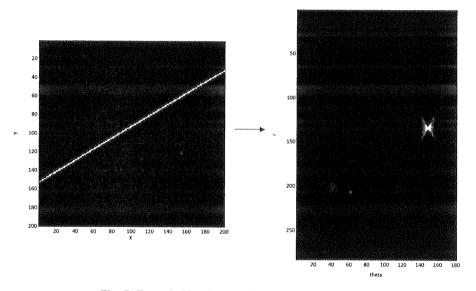

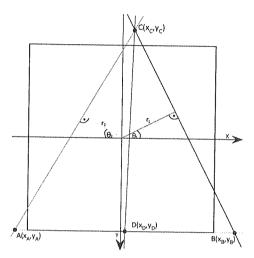

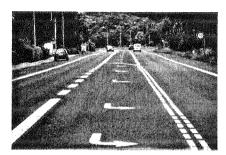

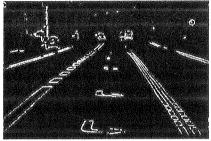

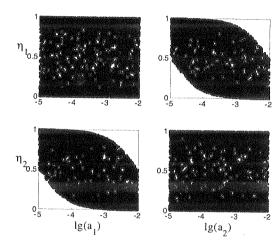

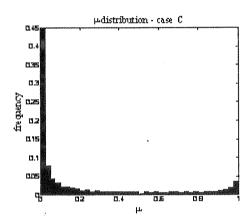

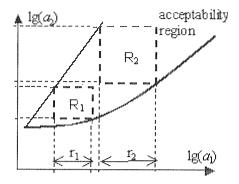

To evaluate our control data graph extraction tool we choose the differential equation integrator circuit. Fig 8. shows its high level asynchronous description with related primary extracted CFG and DFGs with no optimization. Table 2 shows extracted parameters of CFG and DFGs before and after optimization. In this table "Control blocks" is a construction used in CFG. And "operation" is an arithmetic or logical operation that was used in DFGs. In addition to the proposed intermediate representation for DFGs (in Fig 8.c), our tool generates DFGs in a visualized format of dot.

| DFG;000;<br>IN;x;w_001;8;<br>IN;dx;w_002;8;<br>IN;a;w_004;8;<br>OUT;t_000;w_005;8;<br>+ w_003 w_001 w_002<br><w_005 w_003="" w_004<br="">GFD;<br/>DFG;001;<br/>IN;x;w_006;8;<br/>IN;dx;w_007;8;<br/>OUT;x1;w_008;8;<br/>+w_008 w_006 w_007</w_005> | DFG,003; IN;u;w_014;8; IN;3;w_015;2; IN;x;w_016;8; IN;dx;w_019;8; IN;3;w_022;2; IN;y;w_023;8; OUT;u1;w_026;8; *w_017 w_015 w_016 *w_018 w_017 w_014 *w_020 w_018 w_019 -w_021 w_014 w_020 | MOD:0;Pt;X;8;Pt;Y;8;Pt;U;8;Pt;DX;8;Pt;A;8;AO;Uo;8; THR; V_DCL;x;8; V_DCL;y;8; V_DCL;u;8; V_DCL;a;8; V_DCL;a;8; V_DCL;a;8; V_DCL;u;1;8; | #include "asynch.h" #include ssystemc.h> SC_MODULE(diffeq){ public. APAS_IN <sc_uint<8>&gt;X,Y,U,DX,A; AACT_OUT ssc_uint&lt;8&gt;&gt; Uo; SC_CTOR(diffeq) { SC_THREAD(main); } void main(){ sc_uint&lt;8&gt; x,y,u,dx,a,x1,y1,u1; while (true){ PAR_PAS_READ(X,x,</sc_uint<8> |

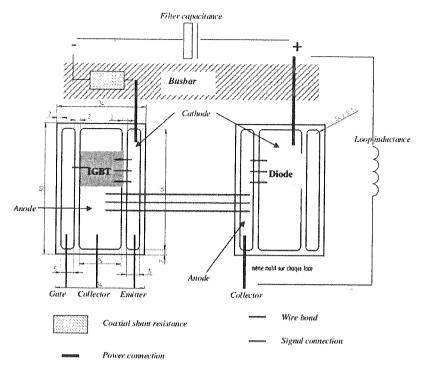

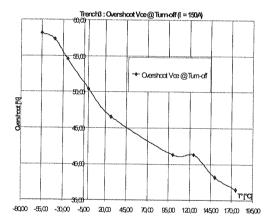

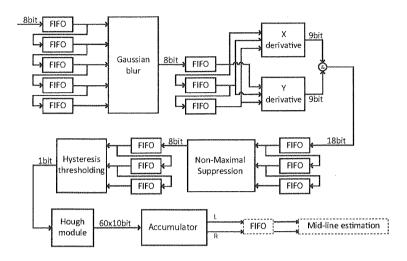

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|